Mise en parallèle de 24 doigts pour augmentation du calibre en courant du JFET diamant

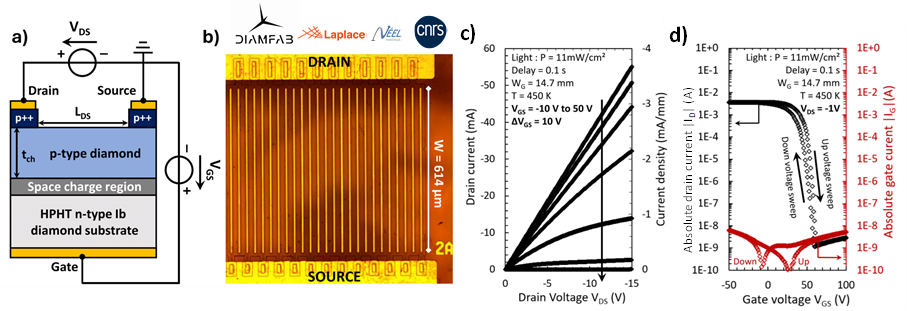

Schéma en coupe du transistor, b) vue de dessus au microscope optique, c,d) caractéristiques mesurées Id=f(Vds,Vgs) et Id,Ig=f(Vgs).

Des transistors en diamant synthétique, bien que peu nombreux, ont déjà été démontrés expérimentalement dans plusieurs groupes dans le monde, et selon différentes architectures. La plupart des transistors à effet de champ (FET) en diamant ayant les meilleures performances s’appuient sur une fine couche conduction dans un gaz de trous (2DHG), issue d’une terminaison de surface diamant de type hydrogénée. Néanmoins, cette architecture peut poser des limites en termes de maîtrise de la conductivité du canal, la reproductibilité de fabrication, son évolutivité et la fiabilité. Les autres transistors utilisant une conduction volumique sont limités par l’homogénéité des couches, et par des développements de grilles faibles limitant alors les courants totaux entre quelques dizaines de nA, 100 µA et au maximum 10 mA.

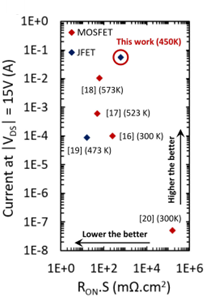

Afin de tirer profit des propriétés électriques du diamant dopé au Bore (type P), une avancée majeure a été obtenue en vue de l’augmentation du calibre en courant de transistors à effet de champ utilisant une conduction volumique (JFET), et grâce au savoir-faire de la start up DIAMFAB sur la croissance homogène de diamant : une largeur de grille totale de 14,7 mm, avec 24 doigts parallèles et un courant supérieur à 50 mA à VDS = -15 V, VGS = 0 V, à 450 K et sous illumination, qui est la valeur la plus élevée rapportée pour un FET en diamant à conduction volumique. Sa résistance spécifique à l’état passant et sa tension de seuil sont respectivement de 608 mΩ.cm², 50 V.

Ces travaux sont issus du projet européen DCADE (Cleansky) et de la thèse CIFRE/ANRT de Damien MICHEZ, et complète les travaux du projet ANR LSDMOS PRCE. La contribution du Laplace (groupe CS) réside dans le dimensionnement, la simulation électro-thermique, la conception et l’optimisation des transistors (jeux de masques, cellule et parallélisation), la prise en compte des contraintes de l’application, ainsi que leur implémentation dans des cellules de conversions. Ils s’inscrivent dans une collaboration de longue date avec l’institut Néel (UPR CNRS, Grenoble) et la startup DIAMFAB depuis sa création en 2019.

D’autres travaux sont en cours, s’appuyant sur l’augmentation du calibre en courant pour aller vers une augmentation de la tenue en tension, sur des architectures à grille à jonction (JFET) ou MOS (MOSFET), et des conductions latérales et verticales. Des applications dans tous les domaines de la conversion sont envisagées, comme par exemple dans le véhicule électrique, l’aéronautique et spatial.

Positionnement des résultats obtenus par rapport à l’état de l’art de transistors diamant à conduction volumique. Courant total en fonction de la figure de mérite RonS, résistance spécifique à l’état passant.

Contacts

Laplace/Groupe CS : Nicolas ROUGER, Directeur de recherche CNRS, responsable groupe CS

Nicolas.rouger@laplace.univ-tlse.fr

DIAMFAB : Juliette LETELLIER, R&D Manager

juliette.letellier@diamfab.com

UGA/CNRS/Néel groupe SC2G : Julien PERNOT, Professeur, directeur adjoint partenariat et valorisation, Institut Néel

Liens externes

Publication scientifique : https://hal.science/hal-04687646

Damien Michez, Juliette Letellier, Imane Hammas, Julien Pernot, Nicolas C. Rouger. Over 50 mA current in interdigitated diamond field effect transistor. IEEE Electron Device Letters, Volume: 45, Issue: 11, November 2024, https://doi.org/10.1109/LED.2024.3453504 . ⟨hal-04687646⟩

Projet européen DCADE Clean Aviation (coordonné par SKLE, Espagne) : https://cordis.europa.eu/project/id/101007868/results/fr

Communiqué DIAMFAB : https://www.linkedin.com/posts/diamfab-grenoble_over-50-ma-current-in-interdigitated-diamond-activity-7244246732627148801-qFzF?utm_source=share&utm_medium=member_desktop

Projet ANR LSDMOS PRCE coordonné par CNRS/Néel : https://anr.fr/Projet-ANR-21-CE50-0036